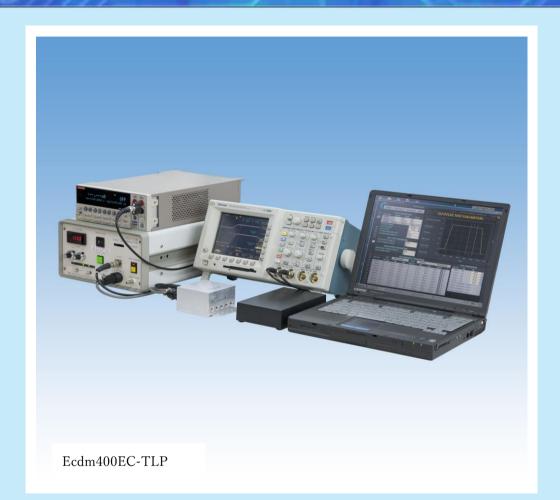

# Evaluation device for "snack back characteristics" Ecdm400EC-TLP

# Features and functions

- Snapback curve measurement

- Resistance test of protection Circuit is possible

- Correlation with ESD test (HBM/MM)

- Maximum high voltage value up to 4kV

- ■Maximum 6A current output

- ●Two kinds of rise time: high speed/medium speed

- ◆Pulse width (50ns 100ns 150ns 200ns)

- Pulse current monitor

- Wafer test jig (optional)

- High-speed current pulse application (option)

# **Application example**

●ESD protection circuit analysis ●ESD tag evaluation ●Quality assurance test

URL http://www.tet.co.jp

# **Test outline**

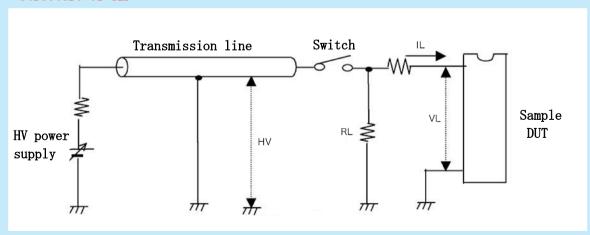

This test equipment is a snapback characteristic analysis tester that can measure the protection circuit against electric discharge of semiconductor and perform stress test. You can apply a constant current to the sample, measure the diode curve of the protection circuit, and perform the electrostatic breakdown test of the device that correlates with the ESD test. Since the electric charge stored in the cable of the lance mission line is applied to the sample with a rectangular wave current pulse, the voltage/current characteristics of the sample are clarified, which is useful for improving the protection circuit and foreseeing development.

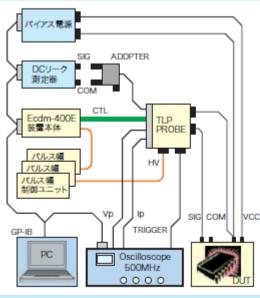

#### **TLP Test**

#### Constitution

- ① Oscilloscope

- ② Ecdm-TLP (main body)

- ③ TPL probe

(With current monitor and waveform monitor)

- 4 Transmission unit

- (5) PC

- 6 Leak current measuring device

## Transmission unit (example)

- ① For 50 nS pulse width

- 2 For 100 nS pulse width

Test configuration diagram

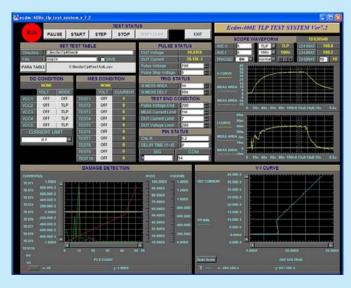

Test PC screen

# Characteristic test of electrostatic discharge protection circuit by TLP pulse

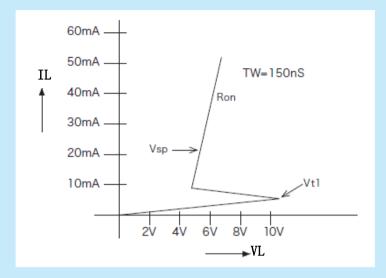

## NMOS Snap-Back Characteristic

## Current pulse Linearity characteristics

H=25nS/divV=250mA/div

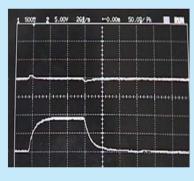

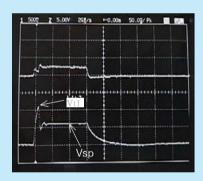

## Snapback characteristics of sample IC

Top: Current waveform Bottom: Voltage waveform

Before snapback

Snapback Vsp occurs

Ron observation

## Structure of TLP

# **Specifications**

■High voltage

Set with potentiometer (2 ranges)

- $\bigcirc$  0 to  $\pm 400$ V (LOW RANGE)

- ② 0 to  $\pm 4$ KV (HIGH RANGE)

- Polarity

- : Switchable by positive or negative switch

- ■Number of discharges

- : 1 to 99 times (00 consecutive) 2-digit digital switch

- ■Display

- (1) High voltage setting panel meter

- ② Charge/discharge LED display

- ■Start test

- : Start/Stop switch

- ■Safety measure

- : Output enable switch

- : With rest strap terminal

- ■TLP probe

- : WT-6NM (with judgment relay)

- : 1 unit with current/voltage detection

- ■TLP specifications

- ①Maximum charging voltage ±4KV

- ②VL voltage 0 to  $\pm 2$ KV

- ③IL current 0 to  $\pm 6A$

- 4Rise time 10nS or less

- ⑤Pulse width By PW pulse width transmission unit.

- ■Accessory: foot switch

- Power supply: AC100V-240V/4A

- ■External dimensions

- ① Unit body: Approx. 257W x 362D x 145H (mm)

- ② TLP probe: Approx. 25 W x 17 D x 148 L (BOX type) mm)

Equipment specifications are subject to change. Please check the latest specifications.

1---1---

Inquiry

### \* Option

- ① TLP probe

- WT-6N (without judgment relay) Tr: 5nS

- Other ultra-high speed TLP unit Tr: 200pS or less

- Wafer TLP probe (manipulator/with L-shaped bracket)

- ② Transmission unit TPU-200N (Tw:200nS)

- ③Transmission unit TPU-150N (Tw:150nS)

- 4 Transmission unit TPU-100N (Tw: 100nS)

- ⑤Transmission unit TPU-50N (Tw:50nS)

- ⑥ Two DUT connection clips

- (7) GP-IB control

- TLP test program

- 10 PC and peripheral devices

#### Other TLP Model

# Ecdm400EC-VF-TLP

Characteristic analyzer of ESD protection circuit for CDM pulse

| tet   | 東京電子交易株式会                  | 社    |

|-------|----------------------------|------|

| TOKYC | ) electronics trading co., | LTD. |

TEL: 042-548-8011 FAX: 042-548-8013

URL http://www.tet.co.jp