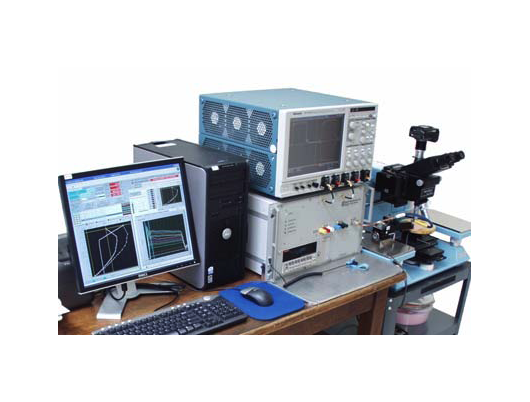

4012 VFTLP+測試系統是在2000年初開發的,目的是在通常的I-V圖中加入高速測量,測量和記錄真正的TDDB波形,從而導致氧化層失效。

Barth公司最終確定了對這壹波形的精確測量,而CDM保護現在可以基於已知的維度設計參數。我們確定了您的CDM保護電路的響應,它具有100個ps的上升時間脈沖,模擬真實的CDM測試。這是提供門級氧化物威脅電壓數據的唯壹方法。

方便、精確、可重復操作

計算機控制的自動測試

測試脈衝寬度:1ns,2ns,5ns,10ns(標準)。脈寬軟件可選。

測試脈衝電壓:0-500V@50Ω負載,1000V@開路

測試脈衝電流:0-10A@50Ω負載,20A@短路

測試脈衝上升時間:100ps,200ps,400ps(內置,軟件可選)

漏電壓:0-100V(0.1V步徑)

漏電流靈敏度:1 pA to 2.5 mA