Model 7000 ESD/Latch-up Test System

Pulse and ESD Technology

# 1024 pins ESD/Latch-up Tester Model 7000-1024 Specification and Technical Information

Tokyo Electronics Trading Co., Ltd 8-26, 4 Chome, Nishiki-cho, Tachikawa-shi Tokyo 190-0022 Japan Tel:+81-42-548-8011 Fax:+81-42-548-8013 URL : www.tet.co.jp

#### 1. Specifications

1.1 ESD Simulation

- Pin Selection Method

E & EL type : Automatic by 2 axes robot

L type : Manual

- High Voltage

E & EL type : ±1000/4500/(8000)V, 1%±5V

L type : ±1000V, 1%±5V

- CR Unit : HBM, MM and others

- ESD Repetition : 1 ~100 times

- ESD Period : 300ms ~ 5s, 100ms increment

- Charge removal : 3 ways selected by program

- 1.2 DC measurement

- $V_{cc1}$  Power Supply(Used as pulsed power supply, as well) Voltage Range : ±30V, 50mV increments Current Measurement : ESD Test : ±500mA, 100nA(Min.) resolution Latch-up Test : ±1000mA, 1mA(Min.) resolution Current Limiter : 50mA ~ 1000mA, 10mA increments Pulse Width :  $0.1 \text{ms} \sim 5 \text{s}$  $T_r, T_f: 3\mu s/V$ Latch-up definition current :  $I_{CCQ} \times N + Offset$ I<sub>CCQ</sub> : Quiescent current Ν : 1~100 Offset: 5mA ~ 1000mA. 5mA increments DUT connection : Automated  $V_{cc2 \sim 4}$ (DC Power Supply) Voltage Range : ±15V, 50mV increments

- Current Measurement : Same as  $V_{cc1}$ Current Limiter : Same as  $V_{cc1}$ Latch-up definition current : Same as  $V_{cc1}$ DUT connection : Automated

- VF/IM(Voltage Force/Current Measurement) Voltage Range : ±15V, 10mV increments Current Measurement : 100mA, 10nA(Min.) resolution

- Current Range : 5 Auto-ranges Averaging : 1, 2, 4, 8, 16, 32 times DUT Connection : Automated

- DVM(Digital Voltmeter)

Voltage Measurement : ±30V, 10mV (Min.) resolution

Input impedance : Over 10MΩ

DUT Connection : Automated 1.3 Latch-up Trigger Source • i<sub>p</sub>(Current Pulse) Generator Current Range : ±1000mA, 1mA(Min.) increments Voltage Measurement : ±30V, 50mV resolution Clamp Voltage :  $1 \sim 30V$ , 0.1V increments Pulse Width : 0.1ms ~ 1s, 0.1ms increments  $T_r$ ,  $T_f$ : about 10µs/200mA Repetition :  $1 \sim 100$  times Period : 100ms ~ 10s, 100ms increment DUT Connection : Automated v<sub>p</sub>(Voltage Pulse) Generator Voltage Range :  $\pm 30V$ , 50mV increments Current Measurement : ±1000mA, 1mA(Min.) resolution Current Limiter : 50mA ~ 1000mA, 10mA increments Pulse Width : 0.2ms ~ 5s, 0.2ms increments T<sub>r</sub>, T<sub>f</sub>: about 50µs/10V Repetition :  $1 \sim 100$  times Period : 100ms ~ 10s, 100ms increment DUT Connection : Automated 1.4 DUT Stabilization Pull-up/down Connected to  $V_{cc1\sim\!\!4}$  , GND, VUD1~VUD3 or maxLogicHi/minLogicLo via 10kΩ. DUT Connection : Automated Multi-channel Control Power Supply Channels: 4 Voltage Range : ±30V, Potentiometer control Voltage Display : 3.5 digits LED with polarity Current: 10mA Current Measurement : 3.5 digits LED with polarity 4 Channels Clock Generator Period, Frequency: CH1: 10k, 100k, 1MHz selectable CH2: Invert of CH1 CH3 :  $1\mu s \sim 100 \ \mu s$ ,  $1\mu s$  increments CH4 :  $1\mu s \sim 100 \ \mu s$ ,  $1\mu s$  increments Output Level : 1V ~ 15V, 0.1V increments DUT Connection : Manually by jumper leads

16 Channels Pattern Generator Channels : 1 Clock Channel 16 Pattern Channels

- Clock : 1μs ~ 100 μs, 1μs increments or 100Mz (optional)

Pattern Timing : Clock Synchronous

Pattern Depth : 1024 vectors

Pattern Group : 2(A and B)

Output Pattern :Only B or B × n after A

Output Level : 1V ~ 15V, 0.1V increments

DUT Connection : Manually by jumper leads

- 1.5 Other Options Temperature controlled Oven : Room temp., +25° ~ 125°C

- Emission Microscope Digital Oscilloscope 1.6 Dimension, Power Requirement Main Body Size : Approx. 1100(W), 900(H),

- Main Body Size : Approx. 1100(W), 900(H), 800(D) mm Main Body Weight : Less than 200kg AC Supply : 100V ±10%, 50/60Hz, Single Phase 1.5kVA(MAX.) Ambient Temperature : +10° ~ 40°C (note) : Other AC supply voltage may be ordered as an option.

- 2. Features

- Up to 1024 pins with full pin combination capability

- Allows ESD(HBM and MM) and Latch-up Tests

- Meets JEDEC, MIL, ESD Association and EIAJ standards, as well as future standards

- Drastic Test Time Reduction

- True constant current pulse and fast pulsed power supply

- Stabilizes DUT by pull-up/down and pattern generator

- Collects detail test results quickly by auto or manual operation

- Allows temperature coefficient test

- Minimum path resistance of power supplies

- Damage detection between tests

- Discharge between zap(s)

- Tests multiple DUT, multiple supply DUT and LCD drivers

- Function test available

- Low insertion force connectors on DUT board

- Complete diagnostics and easy maintenance

- Connectable with Ethernet

- Allows data manipulation by the data base program

#### 3. General

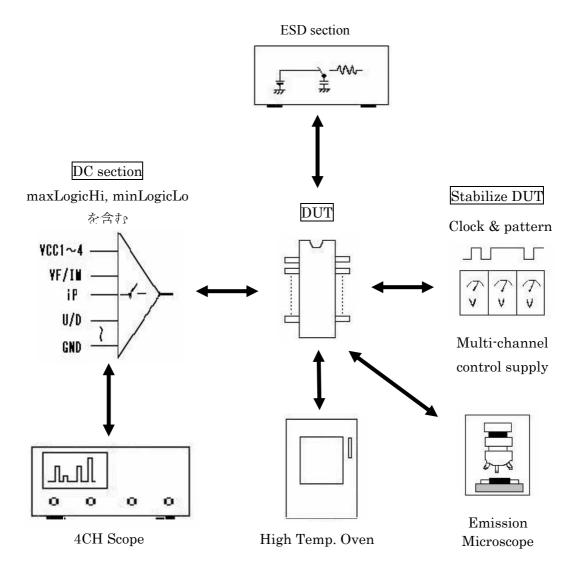

Higher integration and higher speed are increasingly developed day by day in the semiconductor market. It is especially drastic in memory, microprocessor, ASIC and LCD driver. Therefore, the reliability evaluation against ESD(Electro-Static Discharge) and Latch-up of these semiconductor devices is becoming more important. Model 7000 series targets all of these tests by a single system. It allows latch-up test of CMOS LSI with multiple power supply.

The Model 7000 series is a states of the arts reliability evaluation system that allows fully automated ESD test and Latch-up test up to 1024 pin devices. 3 types are available for the series.

#### Type E : ESD test only

#### Type L: Latch-up test only

#### Type EL : Both ESD and Latch-up test

#### • ESD test

ESD Pulse Generator (EPG) unit is attached to a 2 axes robot. The ESD pulse generated in the unit zaps DUT and returns to the unit with the minimum path length so that HBM, MM or other waveform specification may be installed. Each EPG unit includes 4 C/R and the system may have up to 4 robots (256 pins/robot). This means high speed zapping (more than 10 times faster than the predecessor) is available, maintaining zapping period to the same pin enough long as specified by the standard.

Though the Model 7000 adopts robots to define zapped pin, the return or common pin can be programmed

because relay matrix is installed for it. This allows full pin combination ESD test requested by the standards. Degradation or breakage is detected by the measurement function included in the DC section.

- V-I curve variation(% method) before and after zapping

- against DC specification (M/M method) after zapping

- V-I curve is available for every pin and ESD voltage

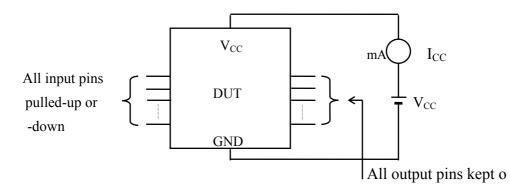

#### Latch-up test

For latch-up test using trigger source such as current pulse  $(i_p)$ , voltage pulse  $(v_p)$  or supply pulse  $(V_p)$ , only DC section is used. For latch-up test using trigger source such as ESD pulse or transient pulse, ESD section is used as well.

Except the  $V_p$  latch-up test, high speed successive approximation procedures are available, to reduce test time. Because latch-up detection is done by comparison between the quiescent  $I_{cc}(I_{ccq})$  and  $I_{cc}$  after the trigger or by the absolute value of  $I_{cc}$  after the trigger, it is important to stabilize the DUT. For this purpose, Model 7000 allows to pull-up or pull-down every input pin, or supply clock or digital pattern by the stabilization section. High temperature oven enables temperature coefficient measurement of latch-up.

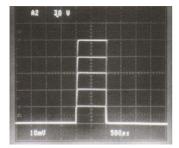

Digitizing oscilloscope will give the waveform information how latch-up proceed.

Emission microscope gives visual data and hard copy of on-chip heat generation because of latch-up.

# Block Diagram

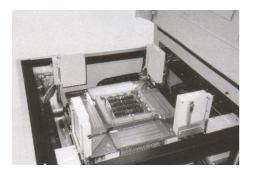

## Position Control by miniature linear guide

**DUT Ejection Mechanism**

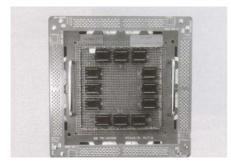

**Multiple Devices DUT Board**

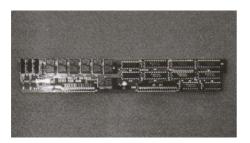

**Pin Electronics**

4. ESD Test (Model 7000E, EL type)

#### 4.1 General

Up to 4 EPG(ESD Pulse Generator) units can be flexibly controlled. Time spent for zapping is reduced down to less than 1/10 of predecessor.

- High speed zapping

- Double buffer mechanism

- 4 generators/unit

- 4 units/system

Easy ejection of 512 pins DUT board

- Miss-feed Protection

- 2 sec to eject

- 60kg of ejection force

- Parallel feed/eject

- Space grade connectors adopted

- High reliability, low contact resistance and low insertion force

- Can be used in the oven

- Can be used for both ESD and Latch-up test

- Common pin connection is done automatically or manually

- High Speed ESD mode available

- HBM/MM Mixed zapping to multiple DUT

One small PC board per pin

- Reliable 3A relay for V<sub>cc</sub> and GND

- Very small relay for pull-up/down

- Low impedance path

- Easy maintenance

It was a common understanding that ESD test took long time. Model 7000 challenged the wall, and this is it. Multiple robot and multiple ESD generator in the unit enabled reduction of total time spent for zapping down to less than 1/10 compared to the predecessors.

ESD test standard have been up-graded every 2 or 3 years including waveform and pin combination specifications. Because Model 7000 adopted C/R unit to specify ESD waveform, most future waveform can be generated by modifying the C/R unit.

DC section is redesigned to improve the precision and speed.

#### 4.2 Features

- Meets EIAJ, MIL, ESD and JEDEC standards

- High speed zapping and DC measurement

- Programmable common(return) pins

- 3 discharge methods

- Up to 8kV ESD voltage (Less than 512 pins)

- Easy replacement of C/R units

- High speed and high precision DC measurement

- Flexible test procedure

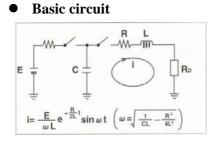

## 4.3 Any ESD Waveform

By developing a C/R unit, any ESD waveform may be generated by the Model 7000 so that a variety of field failure modes may be simulated, especially in Machine Model.

E : High Voltage C : Capacitance

- R : Discharge resistance

- L : Discharge inductance

- $R_D$ : DUT resistance(0  $\Omega$ )

By deciding the L,C,R values, any waveform may be generated, and any failure mode is simulated.

## A. ESD and JEDEC waveform and linearity

| )pF, L=0.75μI | H, R=10Ω         |

|---------------|------------------|

| ips(A)        | tm(ns)           |

| 3.4           | 76               |

| 6.5           | 76               |

| 10            | 76               |

| 13            | 76               |

|               | 3.4<br>6.5<br>10 |

Failure of oxide and junction are mainly simulated.

## B. High stress waveform(customer dependent)

| C=20 | 00pF, L=0.3µH, | R=10Ω  |

|------|----------------|--------|

| E(V) | ips(A)         | tm(ns) |

| 400  | 10             | 54     |

Oxide failure is mainly simulated.

#### C. Thermal stress waveform(customer dependent)

| C=200pF, L= | 7μH, R=30Ω |        |

|-------------|------------|--------|

| E(V)        | ips(A)     | tm(ns) |

| 400         | 1.8        | 760    |

Junction failure is mainly simulated.

#### 4.4 Pin combination test

Common pins can be programmed as TET predecessors. In this method, common pins are automatically changed in sequence. To activate common pin, just enter check (V) in the selection column.

I : Input O : Output I/O : Input/Output

- NC : No Connection

- : Supply Pin

- G : Ground Pin

V

| Zap<br>sequence | Zap pin | Common pin | Selection | Description                                 |

|-----------------|---------|------------|-----------|---------------------------------------------|

| 1               | 1       |            |           | 7                                           |

| 2               | 2       | 3          | v         | Zapped between signal pin,                  |

| 3               | 5       | 3          | v         | supply pin                                  |

| 4               | 6       |            |           | and ground (common) pin                     |

| 5               | 1       |            |           |                                             |

| 6               | 2       | 6          |           | Zapped between signal pin,                  |

| 7               | 3       | 6          |           | ground pin<br>and supply pin                |

| 8               | 5       |            |           | and suppry pin                              |

| 9               | 1       | 2,5        |           | Zannad hatwaan signal nin                   |

| 10              | 2       | 5,1        | v         | Zapped between signal pin<br>and signal pin |

| 11              | 5       | 1,2        |           |                                             |

#### 4.5 3 modes of DUT discharge

It was found that semiconductor device's endurance against ESD depends on DUT discharge method during zapping process. To make clear the dependence, Model 7000 allows 3 modes of discharge. ESD timings are kept as programmed.

Mode 1: Discharge is performed when zapping all selected pins or pin combinations are done.

Mode 2: Discharge is performed when zapping each pin or pin combination is done.

Mode 3: Discharge is performed after every zapping. If 3 zapping is programmed as 3 times at an ESD level, discharge is done 3 times.

#### 4.6 Breakage detection as well as degradation process measurement

Percent method of DC measurement enables device breakage by ESD stress.

Category method of DC measurement enables degradation process of the DUT by ESD stress.

#### A Test result example of percent method

Next Table is an example of print out result. Upper rows are the currents before any zap, and lower rows are the currents at breakage. Breakage is detected by the percentage current change from the current before zap.

| ₽_    | Dev 1        | Dev 2 |        | Dev 3   | Dev      | 4        | Dev 5    | Dev      | 6       | Dev 7   | Dev 8   | 3 D       | ev 9      | Dev 10   | J |

|-------|--------------|-------|--------|---------|----------|----------|----------|----------|---------|---------|---------|-----------|-----------|----------|---|

| Pin # | Name         | DC    | ESD    | Table   | Test 1   | Test 2   | Test 3   | Test 4   | Test 5  | Test 6  | Test 7  | Test 8    | Test 9    | Test 10  | 1 |

|       |              | SRC   | Pulse  | A Table | -500mV   | -400mV   | -300mV   | -200mV   | -100mV  | 100mV   | 200mV   | 300mV     | 400mV     | 500mV    |   |

|       |              | 1.00  |        | B Table | 500mV    | 400mV    | 300mV    | 200mV    | 100mV   | -100mV  | -200mV  | -300mV    | -400mV    | -500mV   | 1 |

|       |              |       |        | C Table |          |          |          |          |         |         |         |           |           |          | 2 |

|       |              |       |        | D Table |          |          |          |          |         |         |         |           |           |          | 1 |

| 1     | Input        | UD1   | #-450  | Vf-A    | -330nA   | 0A       | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 33nA      | 1.2uA    | Ι |

| 1 1   | 2000<br>     |       |        |         | ×-42uA   | ×-34uA   | ×-26uA   | ×-18uA   | ×-9.5uA | *9.7uA  | ×20uA   | *29uA     | *38uA     | ×48uA    | T |

| 2     | Imput        | UD1   | #-750  | Vf-A    | -270nA   | 0A       | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 39nA      | 1.3uA    | T |

| 1 11  |              |       |        | Í Í Í   | ×-450nA  | -15nA    | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 39nA      | 1.3uA    | 1 |

| 3     | Output       |       | #-850  | Vf-B    | 6.6uA    | 160nA    | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | -28nA     | -1.5uA   | 1 |

| 1 1   |              |       |        |         | 8.3uA    | 530nA    | 79nA     | 14nA     | 0A      | 0A      | 0A      | 0A        | 0A        | *-13nA   | 1 |

| 4     | Output       |       | #-450  | Vf-B    | 6uA      | 140nA    | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | -26nA     | -1.4uA   | 1 |

| 1     | 88 - 85.<br> |       |        | 1       | *1.29mA  | *1.02mA  | ×767uA   | *514uA   | *255uA  | *-256uA | ×-512uA | ×-769uA   | *-1.03mA  | *-1.28mA | 1 |

| 5     | Input        | UD1   | #-750  | Vf-A    | -330nA   | 0A       | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 44nA      | 1.3uA    | 1 |

| ( ))  |              |       |        |         | ×-2.78mA | ×-2.21mA | ×-1.66mA | ×-1.11mA | ×-548uA | ×544uA  | ×1.1mA  | *1.65mA   | *2.24mA   | *2.79mA  | 1 |

| 6     | Input        | UD1   | #-850  | Vf-A    | -320nA   | 0A       | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 42nA      | 1.2uA    | 1 |

|       | 1997)<br>    |       |        |         | ×-600nA  | -37nA    | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 33nA      | 1.3uA    | 1 |

| 7     |              | GND   |        |         |          |          |          |          |         |         |         |           |           |          | 1 |

|       |              |       |        |         |          | -        |          | -        |         |         |         |           |           |          | 1 |

| 8     | Imput        | UD1   | #-550  | Vf-A    | -360nA   | 0A       | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 35nA      | 1.2uA    | 1 |

|       |              |       |        | 200     | ×-14uA   | ×-9.5uA  | ×-6uA    | ×-3.4uA  | *-1.4uA | *1.2uA  | *2.4uA  | *3.6uA    | *4.8uA    | *7.3uA   | 1 |

| 9     | Input        | UD1   | #-950  | Vf-A    | -320nA   | 0A       | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 37nA      | 1.2uA    | 1 |

|       |              |       |        |         | ×-480uA  | ×-382uA  | ×-280uA  | ×-184uA  | ×-91uA  | *92uA   | *187uA  | ×288uA    | ×403uA    | *551uA   | 1 |

| 10    | Output       |       | #-750  | Vf-B    | 5.9uA    | 150nA    | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | -29nA     | -1.4uA   | 1 |

|       |              |       |        | 2 2     | *X2.05mA | *X2.05mA | *X2.05mA | *1.57mA- | ×794uA  | ×-787uA | *-1.6mA | *X-2.05mA | *X-2.05mA | *-1.99mA | 1 |

| 11    | Output       |       | #-1100 | Vf-B    | 6.1uA    | 170nA    | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | -31nA     | -1.5uA   | 1 |

| -     | 10 AZ        |       |        |         | ×376uA   | ×294uA   | *221uA   | ×147uA   | *74uA   | ×-72uA  | ×-144uA | ×-218uA   | ×-291uA   | ×-361uA  | 1 |

|       | Imput        | UD1   | #-850  | Vf-A    | -250nA   | 0A       | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 35nA      | 1.luA    | 1 |

| 12    |              |       |        |         | ×-590nA  | -50nA    | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 34nA      | 1.2uA    | 1 |

| 12    | - input      |       |        | 1       | 000 4    | 0A       | 0A       | 0A       | 0A      | 0A      | 0A      | 0A        | 32nA      | 1.2uA    | 1 |

|       | Input        | UD1   | #-750  | Vf-A    | -260nA   |          |          |          |         |         |         |           |           |          |   |

#### B. Test result example of M/M(Min/Max category) method

The table on next page is a test result example of M/M method. From the initial data(before zap) to degrade and breakage process can be listed.

| Dev 1     | Dev  | 2    | Dev 3 | 1    | )ev 4 | De   | v 5 | Dev  | 6   | Dev 7 | 1    | )ev 8 | De  | v 9                                          | Dev 1    | 0 |

|-----------|------|------|-------|------|-------|------|-----|------|-----|-------|------|-------|-----|----------------------------------------------|----------|---|

| ESD Pulse | 1    | 2    | 3     | 4    | 5     | 6    | 7   | 8    | 9   | 10    | 11   | 12    | 13  | 14                                           |          |   |

|           | UD1  | UD1  |       |      | UD1   | UD1  | GND | UD1  | UD1 |       |      | UD1   | UD1 | Vcc1                                         |          |   |

| )         | Vi-C | Vi-C | Vo-B  | Vo-B | Vi-C  | Vi-D |     | Vi-D | ViC | Vo-B  | Vo-B | Vi-D  | ViC |                                              |          |   |

| 0         | EAA  | EAA  | P     | P    | EAA   | EAA  |     | EAA  | EAA | P     | Р    | EAA   | EAA |                                              |          |   |

| -50       | EAA  | EAA  | P     | P    | EAA   | EAA  |     | EAA  | EAA | P     | P    | EAA   | EAA | <u> </u>                                     |          |   |

| -150      | EAA  | EAA  | P     | P    | EAA   | EAA  |     | EAA  | EAA | P     | P    | EAA   | EAA |                                              |          | _ |

| -250      | EAA  | EAA  | P     | P    | EAA   | EAA  |     | EAA  | EAA | P     | P    | EAA   | EAA | <u> </u>                                     | <u> </u> |   |

|           | EAA  | EAA  | P     | P    | EAA   | EAA  |     | EAA  | EAA | P     | P    | EAA   | EAA |                                              |          |   |

|           | EAA  | EAA  | P     | P    | EAA   | EAA  |     | EAA  | EAA | P     | P    | EAA   | EAA |                                              |          |   |

|           | EAA  | EAA  | P     | P    | EAA   | EAA  |     | EAA  | EAA | P     | P    | EAA   | EXA |                                              |          |   |

|           | EAA  | EAA  | P     | P    | EAA   | EAA  |     | EAA  | EXA | P     | P    | EAA   |     |                                              |          |   |

|           | EAA  | EAA  | P     | Z    | EAA   | EXD  |     | EAD  |     | P     | P    | EAA   |     | <u>.                                    </u> |          |   |

|           | EAA  | EXA  | P     |      | EAA   |      |     | EAA  |     | Z     | P    | EAA   |     |                                              |          |   |

|           | EAA  |      | P     |      | EAA   |      |     | EAA  |     |       | P    | EAD   |     |                                              |          |   |

| -1100     | XXX  |      | Z     |      | XXX   |      |     | EXX  |     |       | P    | EXE   |     |                                              |          |   |

#### 4.7 Test conditions are easily made on the Windows 2000 OS

Following figure is an example menu to enter the test conditions of the percent(%) method. 2 or 3 sub-menu complete the programming. Once test is started, test process can be monitored by the display such as zap voltage, pin#, measured value, breakage decision, etc.

Printer, hard disk or floppy disk will save the program and/or test results by operator's request. Connection to the communication line is available.

| IC Name Mc14001b Pin<br>Pin Table C:\Table\Sys\D14Pin.bdf                                                                                                                                                                   | 14 Mut 8 1 2<br>V V                                                                                                                                                                                                    | য য য য                                                                                                                                                                                                         |                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| FileName :         ESD Parameters         Timing         Charge (Sec)         100m         Zap (Sec)         100m         Cycle (Sec)         300m         Amplitude 1 (M)         So         Amplitude 2 (M)         Title | Breakage Criteria       Repetition     3     *       Zap Mode     Pin Scan     ¥       Removal     Alter all pins zppd     ¥       1000     *     100     *       2000     *     200     *       *     200     *     × | Condition Table<br>Condition : C\Table\Cond\14Pin.<br>Clock :<br>ESD Wave Form<br>Vave Form<br>HBM(SP)<br>Polarity Positive<br>Capacitance : 100FF<br>Resistance : 1.5k<br>ESD Simulation<br>Amplitude 100<br>Z | tpf Dpen<br>Dpen<br>Cap Com Seq<br>Gnd : COM1 V<br>Vcc1 : COM1 V<br>Vcc2 : None V<br>Vcc3 : None V<br>Vcc4 : None V<br>Ucc4 : None V |

| Contact Test                                                                                                                                                                                                                |                                                                                                                                                                                                                        | Temp/Hmdty: Wafer Number Lot Number:                                                                                                                                                                            | Execute<br>Test Results                                                                                                              |

#### 4.8 Plentiful Tests

To meet every need of ESD test in semiconductor market, Model 7000 includes following tests that can be used with multiple device DUT board. High speed zapping is also available for all tests.

|    | Test Mode                | Description                                                                                     |

|----|--------------------------|-------------------------------------------------------------------------------------------------|

| 1  | ESD simulation           | Only zapping performed                                                                          |

| 2  | V/I curve measurement    | V/I curves of the DUT are measured                                                              |

| 3* | DC measurement           | DC parameter of the DUT are measured                                                            |

| 4  | ESD Test by % method     | Combination of 1 and 2. Breakage is detected                                                    |

|    |                          | by the current change percentage.                                                               |

| 5* | ESD Test by M/M method   | Combination of 1 and 3. Degradation and<br>breakage are detected by the DC parameter<br>change. |

| 6* | ESD Test by curve tracer | 1 and external curve tracer is used. Operator decide DUT breakage by curve change.              |

| 7  | Contact Test             | Perform DUT contact test.                                                                       |

| 8  | Self Test                | System diagnostics                                                                              |

## 5. Latch-up Test (Model 7000EL, L type)

#### 5.1 General

To get a repeatable test results of latch-up test, following 3 items are important.

- Stable trigger source

- Low impedance latch-up detection power supply

- Stabilize DUT

The Model 7000EL or L are designed in considering all above. The system also look at future upgrade of the relating standards.

#### 5.2 Features

- Meets EIAJ, JEDEC and ESD standard

- Plentiful latch-up trigger source

- Low impedance path and matrix by high current relay

- DUT stabilization by pull-up/down and clock/pattern generator

#### 5.3 Basic timing of latch-up test

• Latch-up process measurement

- Detects temperature dependence

- Connection with emission microscope

- Plentiful test program

- Successive approximation high speed test

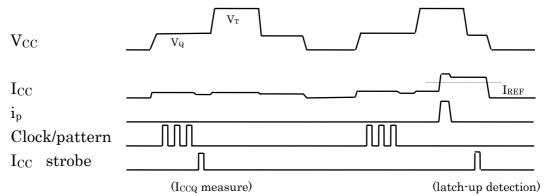

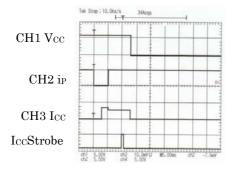

- Next figure illustrates the test timing of current pulse triggered latch-up test.

- $I_{CCQ}$ (quiescent  $I_{CC}$ ) is measured after  $V_Q$  is applied to the DUT supply pins.  $I_{CCQ}$  may be measured after clock and/or pattern are applied to stabilize the DUT, as the figure below.

- Then  $i_p$  is applied to the test pin of the DUT.  $I_{CC}$  is measured after the programmed delay time. If measured  $I_{CC}$  exceeds  $I_{REF}$ (= $I_{CCQ} \times N$  + offset value), latch-up is detected and  $V_{CC}$  is forced to 0V.

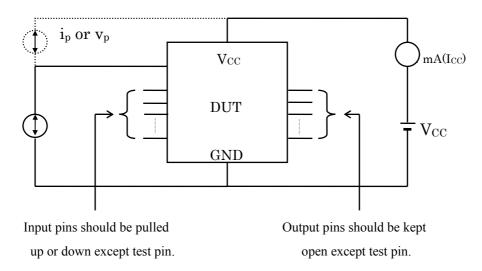

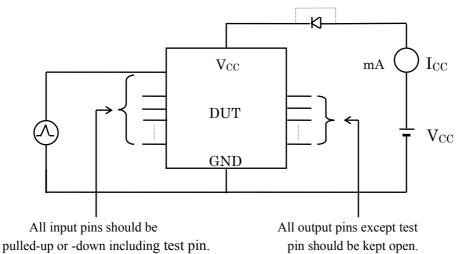

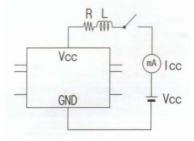

#### 5.4 Latch-up test circuit

Current pulse(i<sub>p</sub>) or voltage pulse(v<sub>p</sub>) triggered latch-up test

• ESD or transient triggered latch-up test

Power supply pulse(V<sub>P</sub>) triggered latch-up test

#### 5.5 Clean Current Pulse

Latch-up repeatability depends on clean trigger source. The current pulse of Model 7000 has less than 5% distortion(overshoot and undershoot) as left picture. Variable  $t_r/t_f$  may be ordered as an option. After the trailing edge of the current pulse, input pin is pulled -up or -down without discontinuity, then  $I_{CC}$  is measured.

#### 5.6 Low power supply bus impedance

Because latch-up current is usually very high, voltage drop of the supply path causes recovery from latch-up, though once latched-up. This is a source of unstable measurement. To avoid it, Model 7000 uses low contact resistance and high current relay to switch  $V_{CC}$  supplies and decreases the impedance of supply path.

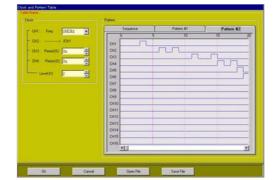

#### 5.7 **DUT stabilization**

This window is to edit digital patterns to stabilize a DUT for ESD and latch-up test. Clocks and patterns are programmed by host PC windows. Higher density DUT needs some digital patterns before  $I_{CC}$  measurement.

#### 5.8 To monitor latch-up process

The analysis of latch-up process has been difficult because the usual tester gives only digital results. Digitizing scope option stores the latch-up process and waveform information is easily collected as this picture. A-D converter board of PC may take over the scope, though bandwidth is limited. With the optional high temperature oven and emission microscope, further analysis such as temperature coefficient or latch-up location detection are possible.

#### 5.9 Test conditions are easily made on the Windows 2000 OS

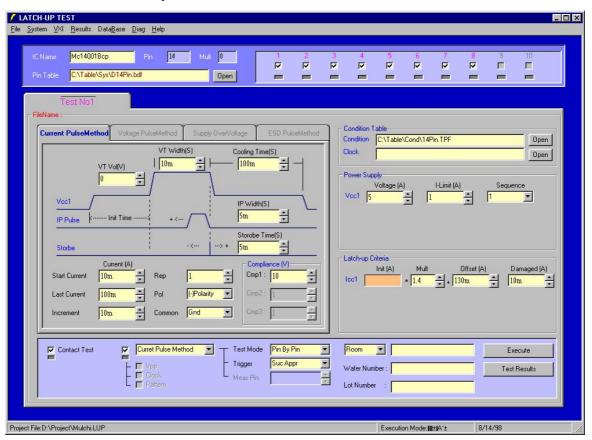

This window and a few sub-windows enable to decide latch-up test conditions and test execution. Up to 10 DUTs are automatically tested. Left window accepts  $i_p$  parameters such as timings, current, etc.,  $V_{CC}$  voltage, sequence, latch-up definition. Pull-up, down, clock and pattern for DUT stabilization are programmed on the sub-windows. Input pins connected to clock or pattern are fixed to the level defined by the condition table during I<sub>CC</sub> measurement.

|                | Test mode                                         | test pin                  |

|----------------|---------------------------------------------------|---------------------------|

| 1              | Current pulse triggered, incremental              | I, O, I/O                 |

| 2              | Current pulse triggered, successive approximation | I, O, I/O                 |

| 3*             | Voltage pulse triggered, incremental              | I, O, I/O                 |

| 4*             | Voltage pulse triggered, successive approximation | I, O, I/O                 |

| 5*             | ESD pulse triggered, incremental                  | I, O, I/O,V <sub>CC</sub> |

| 6*             | ESD pulse triggered, successive approximation     | I, O, I/O,V <sub>CC</sub> |

| 7              | Supply pulse triggered, incremental               | V <sub>CC</sub>           |

| 8*             | Transient pulse triggered, incremental            | I, O, I/O,V <sub>CC</sub> |

| 9 <sup>*</sup> | Transient pulse triggered, successive approx.     | I, O, I/O,V <sub>CC</sub> |

| $10^{*}$       | Punch through current measurement                 | I, I/O                    |

| 11*            | Temperature coefficient test                      |                           |

| $12^{*}$       | Test with emission microscope                     |                           |

| 13             | DUT contact test                                  |                           |

| 14             | Self test, Diagnostics                            |                           |

| I : Inpu       | t pin O : Output pin I/O : Input/Out              | put pin                   |

#### 5.10 Plentiful test modes

V<sub>CC</sub> : Power Supply Pin GND : Ground pin \* : Optional

# 6. System Configuration

Type E : ESD test

Type EL : Both ESD and Latch-up test

Type L : Latch-up test

# 6.1 Pin count : 256/512/ 1024 pins

## 6.2 ESD section

|               | Function        | n                 | Е        | $\mathbf{EL}$ | L          |

|---------------|-----------------|-------------------|----------|---------------|------------|

|               |                 | 1kV               | $\Delta$ | $\Delta$      | NA         |

| Type          | High Voltage    | $4.5 \mathrm{kV}$ | 0        | 0             | NA         |

| E/EL          |                 | 8kV               | Δ        | Δ             | NA         |

| Auto Zap      | Common pin rela | ay matrix         | 0        | 0             | NA         |

| Auto          |                 | HBM               | 0        | 0             | NA         |

| Pin selection | EPG unit        | MM                | 0        | 0             | NA         |

|               |                 | Others            | $\Delta$ | Δ             | NA         |

| Type E/EL     | X,Y axis ro     | obot              | 0        | 0             | NA         |

| Auto Zap      | DUT board       | $256 	ext{ pins}$ | $\Delta$ | $\Delta$      | NA         |

| Auto pin sel. | Loader/unloader | 512/1024 pins     | 0        | 0             | NA         |

| Type L        | High voltage    | e 1kV             | NA       | NA            | $\bigcirc$ |

| Auto Zap      | MPG unit        | MM                | NA       | NA            | $\bigcirc$ |

| Manual sel.   | wir G unit      | Others            | NA       | NA            | Δ          |

# 6.3 DC section

| Functions               | Ε        | $\mathbf{EL}$ | L        |

|-------------------------|----------|---------------|----------|

| VF/IM                   | 0        | 0             | 0        |

| $V_{\rm CC}(V_{\rm P})$ | $\Delta$ | 0             | 0        |

| $V_{CC2}$ ~ $V_{CC4}$   | $\Delta$ | $\Delta$      | $\Delta$ |

| DVM                     | $\Delta$ | 0             | $\Delta$ |

| ip                      | NA       | 0             | 0        |

| Vp                      | NA       | Δ             | Δ        |

| VF/IM self test board   | 0        | 0             | 0        |

# 6.4 Stabilization section

| Functions                                                    | Е | EL | L |

|--------------------------------------------------------------|---|----|---|

| ${ m V}_{ m CTL}(6~{ m channels~control}~{ m power~supply})$ | Δ | Δ  | Δ |

| 4 channels clock                                             | Δ | Δ  | Δ |

| 16 channels pattern                                          | Δ | Δ  | Δ |

| 256 channels pattern                                         | Δ | Δ  | Δ |

| Pull-up/down                                                 | Δ | 0  | 0 |

# 6.5 Other functions

| Е  | $\operatorname{EL}$ | L                                                                      |

|----|---------------------|------------------------------------------------------------------------|

| NA | $\Delta$            | Δ                                                                      |

| Δ  | Δ                   | Δ                                                                      |

| NA | Δ                   | Δ                                                                      |

| NA | Δ                   | Δ                                                                      |

|    | Δ<br>NA             | $\begin{array}{c c} \Delta & \Delta \\ \hline NA & \Delta \end{array}$ |

$\odot$  : Standard  $\Delta$  : Optional NA : Not available